# Characterization of strained silicon FinFETs and the integration of a piezoelectric layer

## CHARACTERIZATION OF STRAINED SILICON FINFETS AND THE INTEGRATION OF A PIEZOELECTRIC LAYER

**Buket Kaleli**

#### The graduation committee consists of:

Chairman: Prof.dr.ir. A.J. Mouthaan University of Twente Secretary: Prof.dr.ir. A.J. Mouthaan University of Twente Prof.dr.ir. R.A.M. Wolters Promoter: University of Twente Asst. promoter: Dr. ir. R.J.E. Hueting University of Twente Referent/expert: Dr. K. Reimann **NXP Semiconductors** Members: Prof.dr. J. Schmitz University of Twente Prof.dr.ing. A.J.H.M. Rijnders University of Twente Prof.dr. D.J. Gravesteijn NXP Semiconductors/ University of Twente

Prof.dr. P.M. Sarro TU Delft

This research was funded by the Dutch Technology Foundation STW, a project "Piezoelectric layer formation on a silicon channel" nr. 10176 and carried out at the Semiconductor Components group, MESA+ Institute of Nanotechnology, University of Twente, The Netherlands.

PhD thesis—University of Twente, Enschede, The Netherlands

Title: Characterization of strained silicon FinFETs and the integration of a

piezoelectric layer.

Author: Buket Kaleli

ISBN: 978-90-365-0471-3

DOI: 10.3990/1.9789036504713

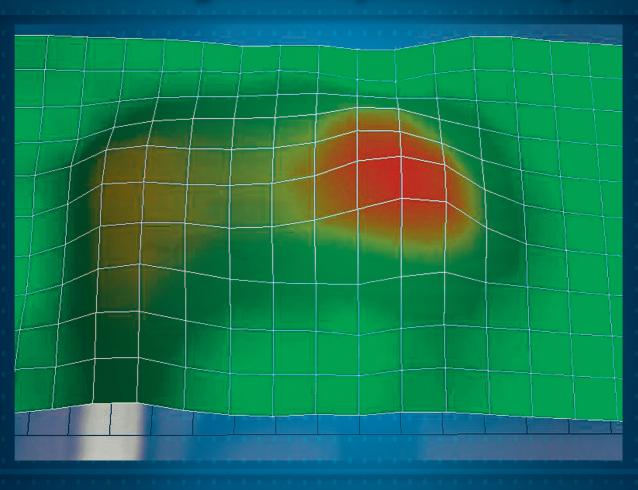

Cover: 2D upward response scan of a PiezoFET with 30 nm fin width (Chapter 5).

Cover designed by Berkay Kaleli.

#### Copyright © 2013 by Buket Kaleli

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, in whole or in part without the prior written permission of the copyright owner.

## CHARACTERIZATION OF STRAINED SILICON FINFETS AND THE INTEGRATION OF A PIEZOELECTRIC LAYER

### **DISSERTATION**

to obtain

the degree of doctor at the University of Twente,

on the authority of the rector magnificus,

prof. dr. H. Brinksma,

on account of the decision of the graduation committee,

to be publicly defended

on Wednesday the 20<sup>th</sup> of November 2013 at 16:45

by

### **BUKET KALELİ**

born on the 24<sup>th</sup> of September 1984 in Eskişehir, Turkey

| This dissertation is approved by:                                                    |

|--------------------------------------------------------------------------------------|

| Drof dr in Dob A M. Moltors (promotor)                                               |

| Prof.dr.ir. Rob A.M. Wolters (promoter) Dr.ir. Raymond J.E. Hueting (asst. promoter) |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

### Contents

| 1. | Introduction                                                                       | 1  |

|----|------------------------------------------------------------------------------------|----|

|    | 1.1 The PiezoFET project                                                           | 2  |

|    | 1.2 Concepts for steep sub-threshold slope FETs                                    | 2  |

|    | 1.3 Choice of device configuration and materials                                   | 4  |

|    | 1.3.1 FinFETs as a replacement of MOSFETs                                          | 4  |

|    | 1.3.2 Encapsulated TiN as a gate material                                          | 6  |

|    | 1.3.3 Converse Piezoelectric effect as a stressor                                  | 7  |

|    | 1.4 Technological requirements and research questions                              | 8  |

|    | 1.5 Organization of the thesis                                                     | 8  |

|    | References                                                                         | 9  |

|    |                                                                                    |    |

| 2. | Strained silicon devices                                                           | 13 |

|    | 2.1 Strain formation in silicon based devices                                      | 14 |

|    | 2.2 The effect of strain on the band gap and mobility                              | 15 |

|    | 2.3 TiN induced strain on FinFETs                                                  | 18 |

|    | 2.3.1 Characterization of strain by optical and its effects by electrical techniqu |    |

|    |                                                                                    | 20 |

|    | 2.3.1.1 Temperature dependent <i>I-V</i> measurements on strained devices          | 21 |

|    | 2.3.1.2 Raman spectroscopy characterization of strain                              | 23 |

|    | 2.3.2 Discussion                                                                   | 30 |

|    | 2.4 Conclusions                                                                    | 30 |

|    | References                                                                         | 31 |

|    |                                                                                    |    |

| 3. | Ferroelectric PZT thin film layers                                                 | 35 |

|    | 3.1 Introduction                                                                   | 36 |

|    | 3.2 PZT capacitors                                                                 | 37 |

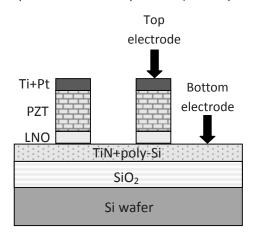

|    | 3.2.1 Capacitor fabrication                                                        | 37 |

#### Contents

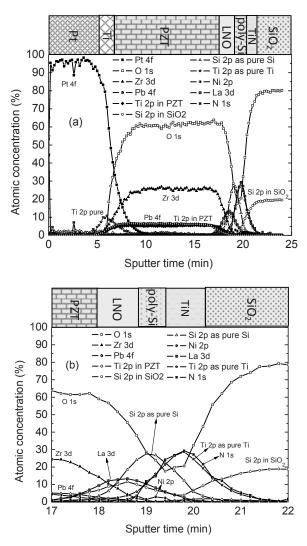

|    | 3.2.2 Characterization of the PZT stacks                                                        |

|----|-------------------------------------------------------------------------------------------------|

|    | 3.2.2.1 XPS depth profile                                                                       |

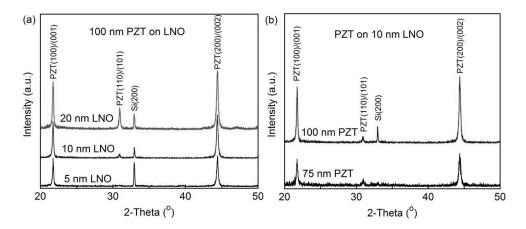

|    | 3.2.2.2 XRD analysis                                                                            |

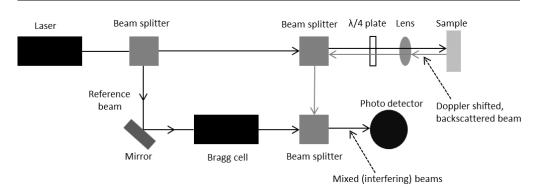

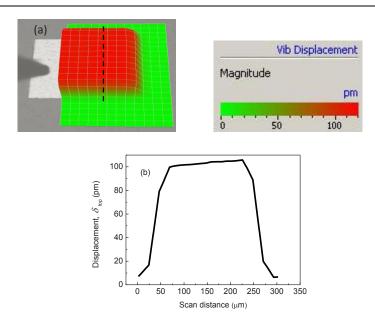

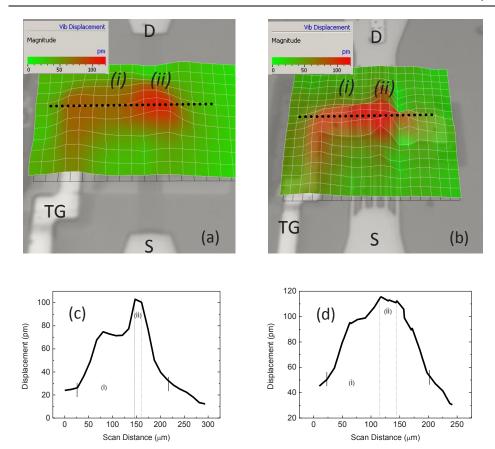

|    | 3.2.2.3 Laser Doppler Vibrometer measurements40                                                 |

|    | 3.2.3 Electric and ferroelectric characterization                                               |

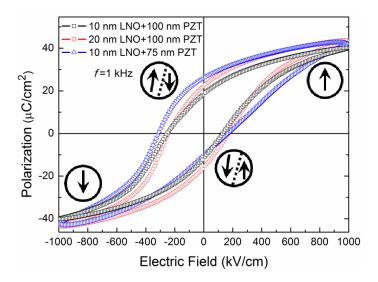

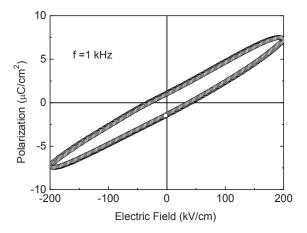

|    | 3.2.3.1 Polarization hysteresis measurements                                                    |

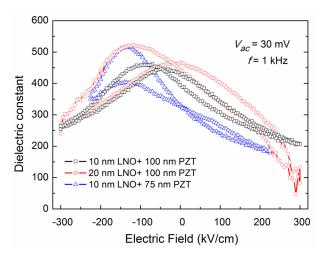

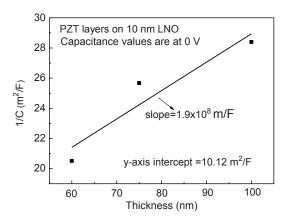

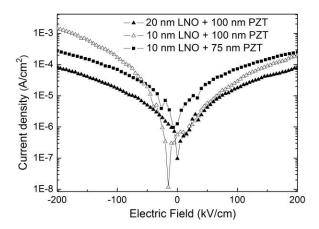

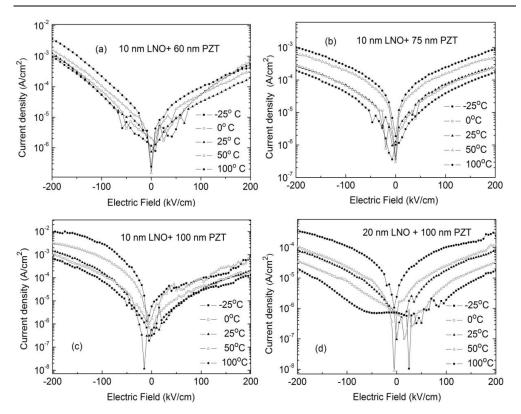

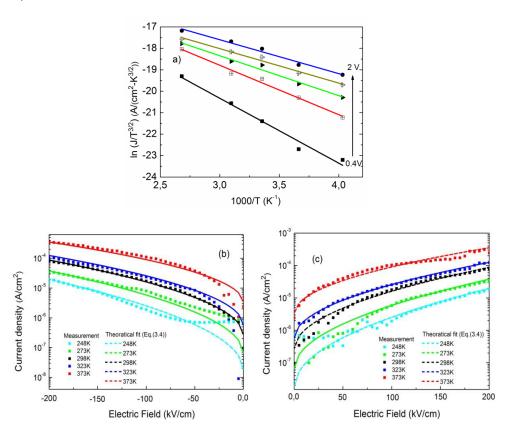

|    | 3.2.3.2 <i>C-E</i> and <i>J-E</i> measurements                                                  |

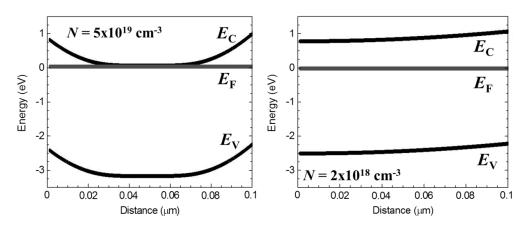

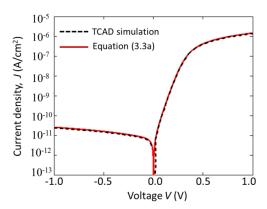

|    | 3.2.3.3 Analysis                                                                                |

|    | 3.3. Conclusions                                                                                |

|    | References                                                                                      |

|    |                                                                                                 |

| 4. | Fabrication and characterization of FinFETs55                                                   |

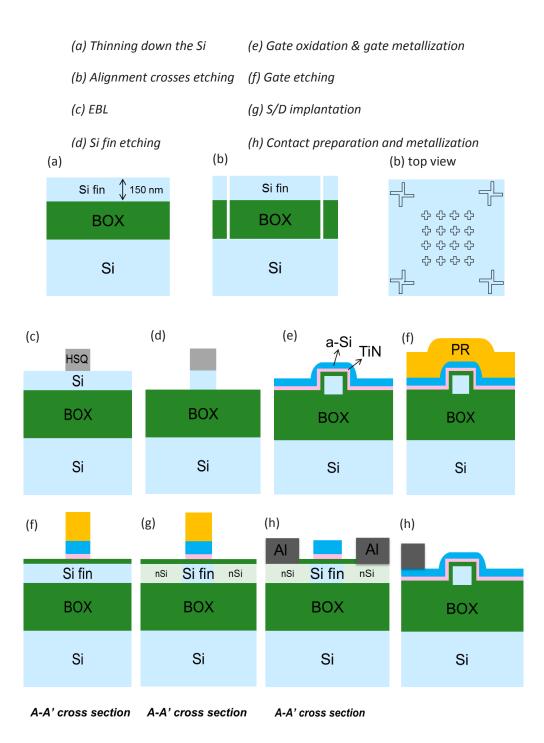

| ٠. | 4.1 Fabrication of FinFETs                                                                      |

|    | 4.1.1 Design                                                                                    |

|    | 4.1.2 Processing                                                                                |

|    | 4.2 Physical and electrical characterization of FinFETs                                         |

|    | 4.2.1 FIB/TEM analysis                                                                          |

|    | 4.2.2 Resistance measurements                                                                   |

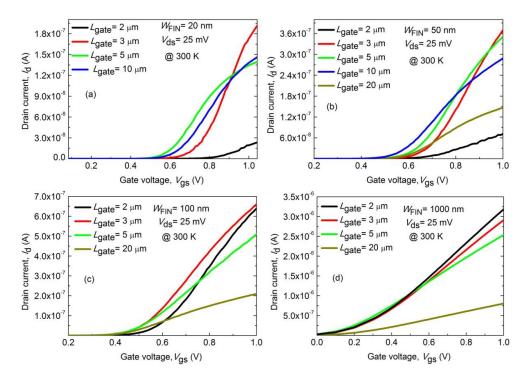

|    | 4.2.3 <i>I-V</i> characterization and analysis                                                  |

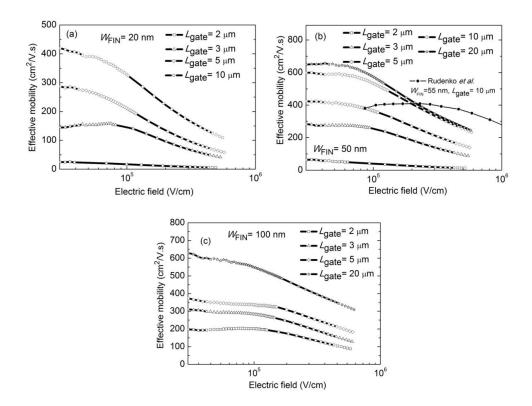

|    | 4.2.4 Mobility calculation                                                                      |

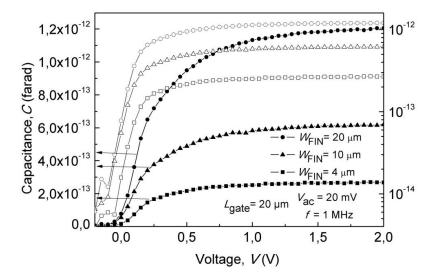

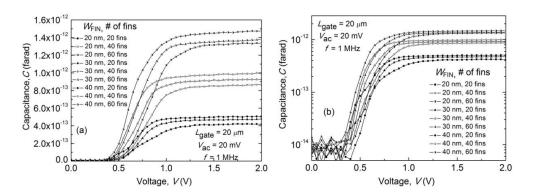

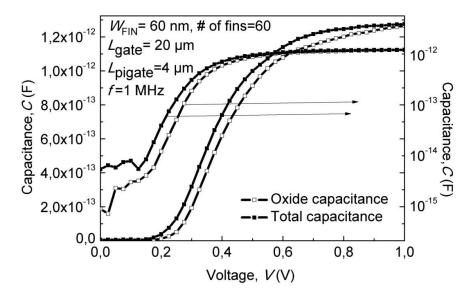

|    | 4.2.5 <i>C-V</i> characterization                                                               |

|    | 4.3 Conclusions                                                                                 |

|    | References                                                                                      |

|    |                                                                                                 |

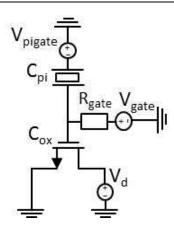

| 5. | The PiezoFET: a piezoelectric layer around a FinFET85                                           |

| ٥. | 5.1 The piezoelectric layer as a stressor                                                       |

|    | 5.2 Processing of the PiezoFET                                                                  |

|    | -                                                                                               |

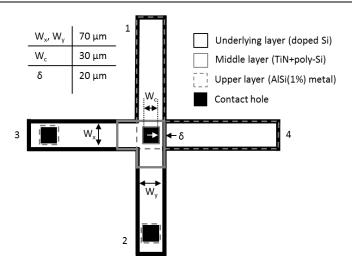

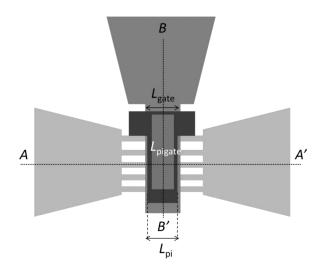

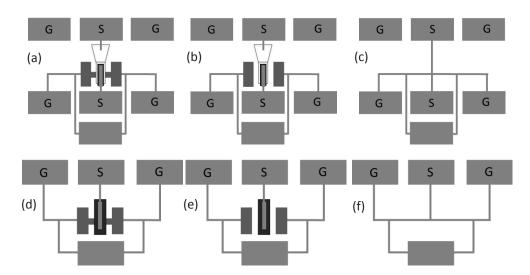

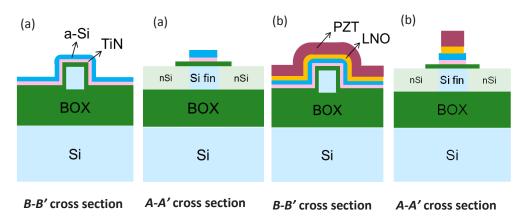

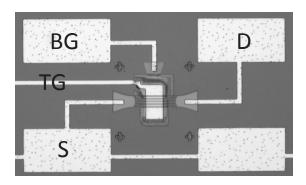

|    | 5.2.1 Mask design       .88         5.2.2 Processing       .90                                  |

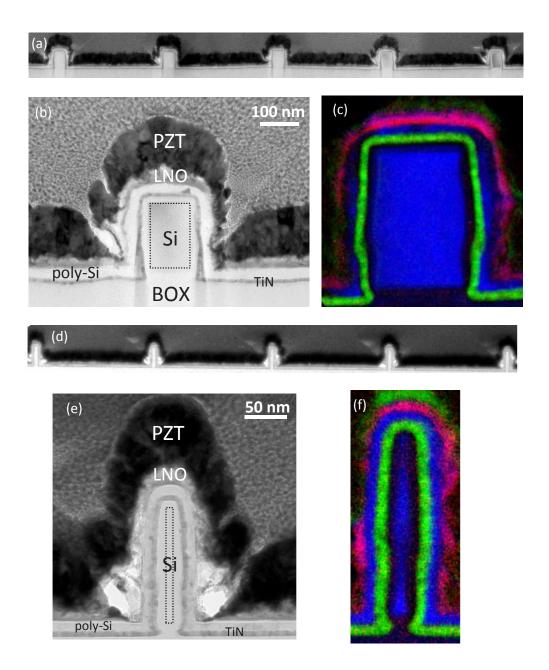

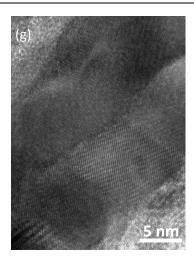

|    | 5.2.2 Processing90 5.3 Physical, optical and ferroelectric characterization of PZT on FinFETs92 |

|    | 5.3.1 TEM analysis                                                                              |

|    | 3.3.1 1 Livi alialysis92                                                                        |

|     | Con                                                                       | tents |

|-----|---------------------------------------------------------------------------|-------|

|     | 5.3.2 Laser Doppler vibrometer measurements                               | 94    |

|     | 5.3.3 Polarization hysteresis measurement                                 | 96    |

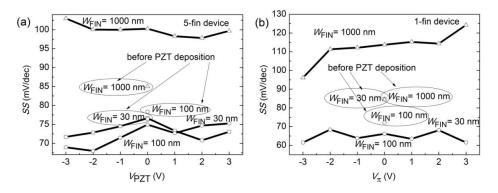

|     | 5.4 Electrical characterization of the PiezoFET                           | 97    |

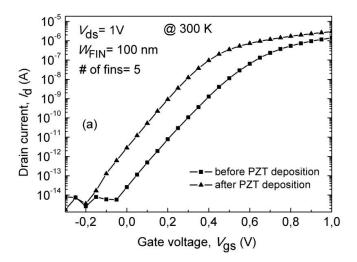

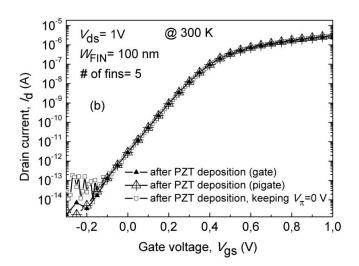

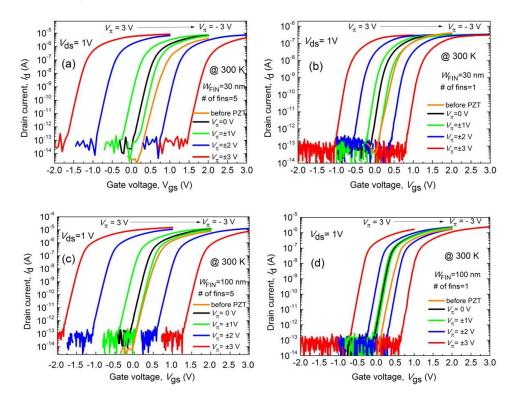

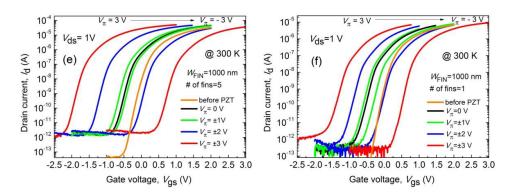

|     | 5.4.1 Effect of the PZT deposition on the $I_{ m d}$ - $V_{ m gs}$ curves | 97    |

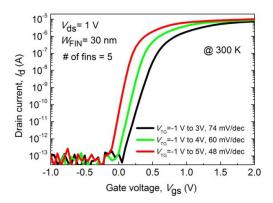

|     | 5.4.2 Effect of PZT biasing on the $I_{ m d}$ - $V_{ m gs}$ curves        | 100   |

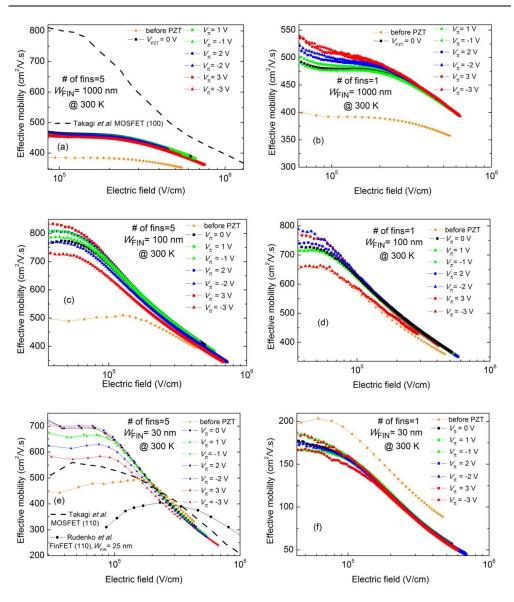

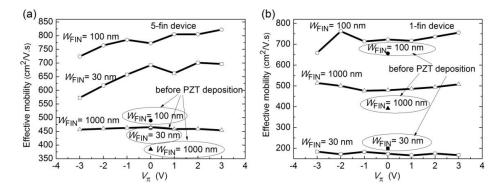

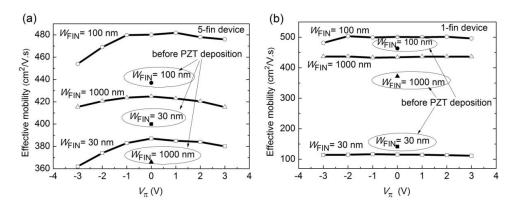

|     | 5.4.3 Mobility calculations                                               | 107   |

|     | 5.4.3.1 Discussion                                                        | 110   |

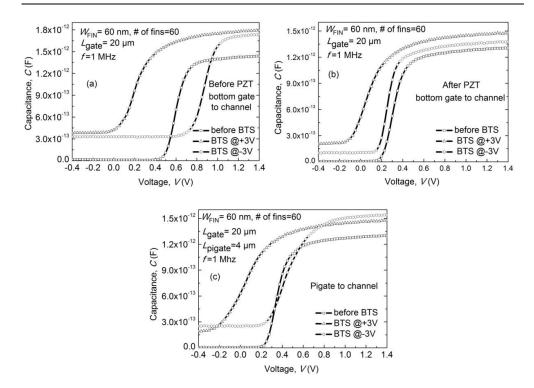

|     | 5.4.4 <i>C-V</i> characterization                                         | 114   |

|     | 5.5 Conclusions                                                           | 116   |

|     | References                                                                | 118   |

|     |                                                                           |       |

| 5.  | Conclusions and recommendations                                           | . 121 |

|     | 6.1 Conclusions                                                           | 122   |

|     | 6.2 Recommendations                                                       | 124   |

|     | Reference                                                                 | 125   |

| Sun | nmary                                                                     | . 127 |

|     | nenvatting                                                                |       |

|     | t of publications                                                         |       |

|     |                                                                           |       |

| Contents | <br> | <br> |

|----------|------|------|

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

|          |      |      |

| x        |      |      |

# 1 Introduction

This chapter presents a general introduction to this thesis. The motivation, the project description and objectives are described. The reasoning behind the preferred device configuration and materials are discussed. Furthermore, concepts of steep subthreshold devices reported from literature are summarized and the effects of strain in the Si channel are addressed. This chapter ends with an outline of the thesis.

#### 1.1 The PiezoFET project

The official title of the project leading to this thesis is "Piezoelectric layer formation on a silicon channel". It basically considers a piezoelectric layer on top of a fin shaped field-effect transistor (FinFET) channel. "PiezoFET" is the name referring to the fabricated device structure in this thesis. The described project is funded by the Dutch Technology Foundation (STW), with project number 10176. During the given period of time, the feasibility of this novel device structure with a piezoelectric stressor has been investigated. This work has been conducted at the MESA+ Institute for Nanotechnology, The Netherlands.

#### 1.2 Concepts for steep sub-threshold slope FETs

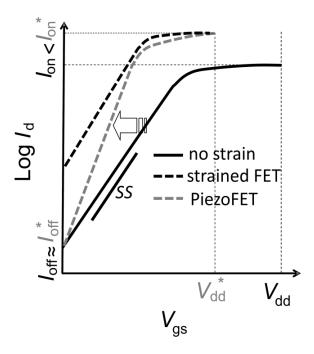

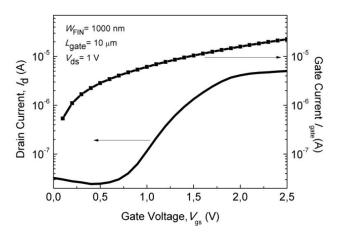

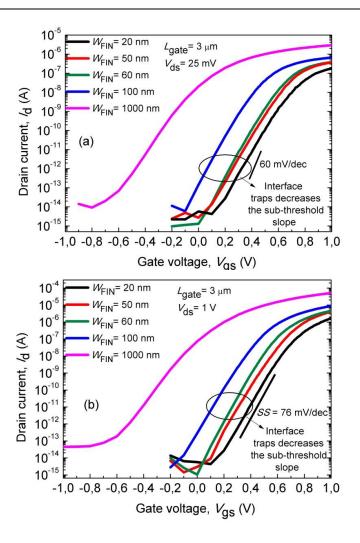

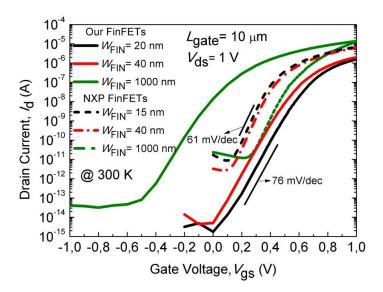

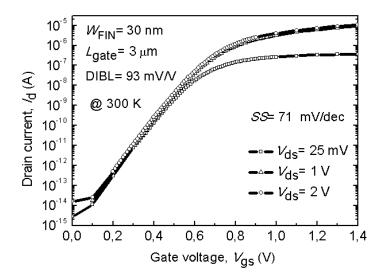

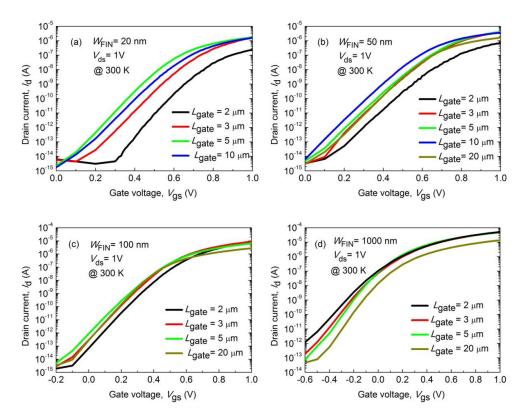

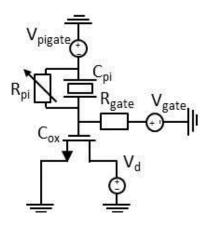

The parameter that quantifies the electrostatic gate control over the sub-threshold drain current ( $I_d$ ) of a FET is called the sub-threshold swing (SS). The SS is, by definition, the change in gate voltage resulting in one order of magnitude change in the drain current, *i.e.* the inverse of the sub-threshold slope. It is presented in Fig. 1.1 (no strain).

Fig. 1.1 Illustration of the  $I_d$ - $V_{gs}$  characteristics of a MOSFET on semi-logarithmic scale. The characteristics are shown for a device with no strain (*i.e.* relaxed condition), constant strain and strain formed by the converse piezoelectric effect (*i.e.* the PiezoFET). The sub-threshold swing (SS) is also indicated.

For an ideal Si transistor, *i.e.* there is good electrostatic gate control over  $I_d$ , the SS equals 60mV/dec at room temperature. In practice this can be obtained for (long channel) fully depleted FinFETs and ultra-thin body SOI MOSFETs where the depletion capacitance is negligible, as will be discussed in chapter 4. Good gate control is important since it reduces the sub-threshold current which in turn determines the leakage power loss [1], an important contribution to the total power loss in a chip. Since, in advanced CMOS technology, there is a continuous trend in increasing functionality and speed of the electronic chip, the power consumption of the transistors should be reduced even more.

For CMOS, the so-called strain, *i.e.* mechanical deformation, is employed in silicon both by the academia and industry to increase the performance at a lower power. The conventional type of strain is typically constant depending on the surrounding materials and leads to a relatively high off-current ( $I_{off}$ ) and on-current ( $I_{on}$ ) provided all other process parameters have been kept the same [2-4], as illustrated in Fig. 1.1 (strained FET).

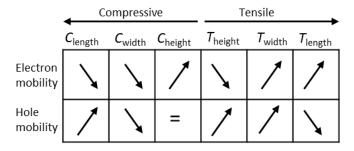

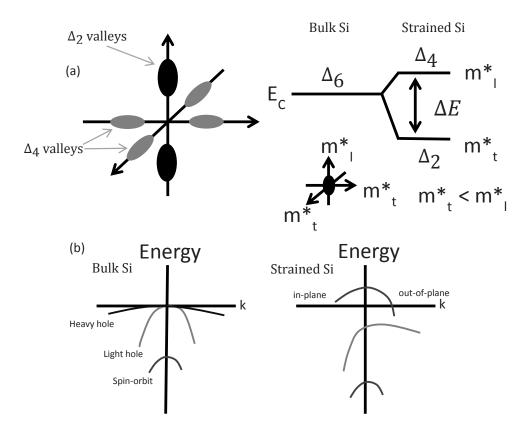

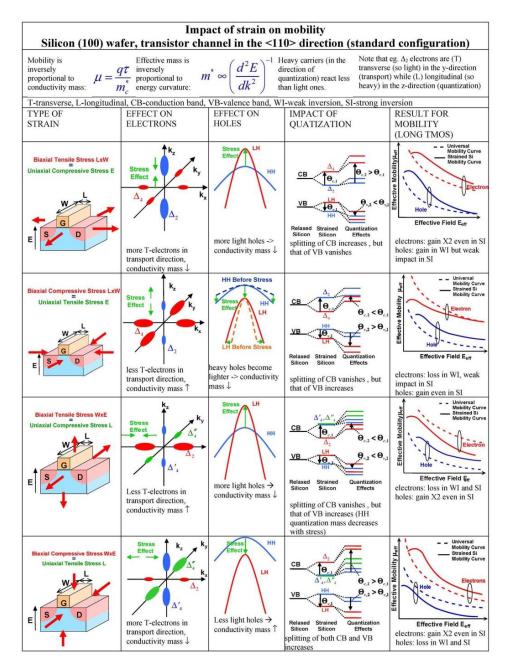

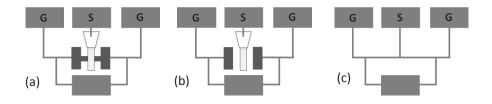

As discussed in chapter 2, the sub-threshold current is exponentially dependent on the band alignment, which is affected by strain formation and leads to an increased  $I_{\rm off}$ . This strain-induced change in band alignment could also lead to increased charge carrier mobility values resulting in a higher  $I_{\rm on}$ . Fig. 1.2 summarizes the effect of the stress components on the mobility in FinFETs (redrawn after [5]). It can be concluded from this figure that, since n-FinFETs are fabricated in this thesis, biaxial tensile stress along the channel length and fin width is favorable.

However, as illustrated in Fig. 1.1 a SS of less than 60 mV/dec, *i.e.* a sub-thermal sub-threshold swing, is desirable. Several device concepts have been proposed to obtain a sub-thermal SS. Tunnel FETs and impact ionization MOSFETs have been reported for this purpose [6-10]. However, there are some challenges like a low on- to off-current ratio  $I_{\rm on}/I_{\rm off}$  and hot carrier effects. In addition, negative capacitance FETs have been demonstrated to decrease the SS by replacing the standard insulator with a ferroelectric insulator [11, 12]. Therefore, before being successfully embedded in the CMOS technology, the gate stack materials and theory need to be studied further.

In this work, we propose and realize a new device concept which makes use of the converse piezoelectric effect to form a strain modulation in a silicon (Si) body. The basic idea behind this concept is that the strain in the Si body is increasing for a higher bias over the piezoelectric layer; that is placed on top of or around a Si body. This device concept is called the PiezoFET. The ideal  $I_{\rm d}$ - $V_{\rm gs}$  characteristic is presented in Fig. 1.1 (PiezoFET).

In the PiezoFET, strain arises due to an upward and downward motion of the piezoelectric layer caused by an external bias. The strain is basically zero in the off-state, meaning that the leakage current does not change compared to a relaxed condition, while in the on-

state, by biasing the piezoelectric layer, a maximum amount of strain is obtained [13]. Consequently, the SS can be reduced by a piezoelectric stressor.

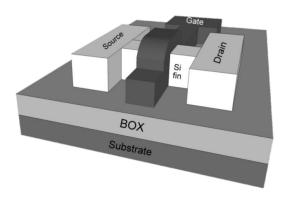

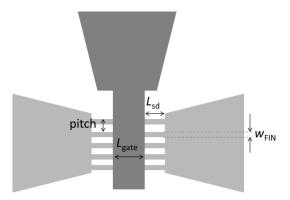

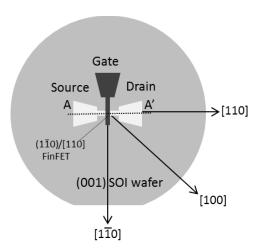

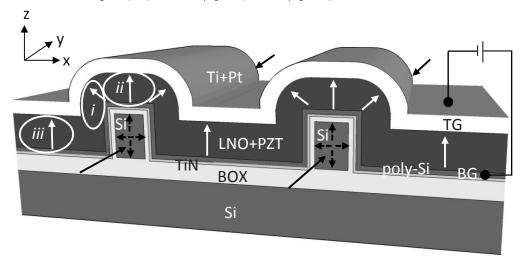

The resulting strain condition is not straightforward since it strongly depends on the (electro-) mechanical properties and layer thicknesses of the surrounding materials. The device geometry is equally important since it determines the (electro-) mechanical boundary conditions. These are different for a planar structure and a 3D structure like a FinFET. In Fig. 1.3 a schematic lay out of an SOI FinFET is presented, showing the Si fin, source and drain and gate configuration on a buried oxide (BOX) layer. Here the fin width, distance between fins and the aspect ratio are important. It is expected that for a high aspect ratio and relatively small fin (and pitch) dimensions strain can be obtained in a FinFET-based PiezoFET. In this case, a piezoelectric layer and electrodes are introduced in the structure to control strain. More analysis on the strain induced by the piezoelectric layer is discussed in chapter 5.

By considering all the strain related effects that have been mentioned until now, the change in the mobility and  $I_{\rm d}$ - $V_{\rm gs}$  characteristics can be estimated. The ultimate goal of the piezoelectric effect induced strain on the  $I_{\rm d}$ - $V_{\rm gs}$  characteristics is illustrated in Fig. 1.1 (PiezoFET).

Fig. 1.2 The effect of stress components on the  $(110)/[1\overline{1}0]$  FinFET electron and hole mobility. Redrawn after [5].

In summary, it is expected that the PiezoFET can offer a great potential as a low-power switch. In this study, the PiezoFET in a fin-shaped field-effect transistor (FinFET) configuration has been realized and analyzed.

#### 1.3 Choice of a device configuration and materials

#### 1.3.1 FinFETs as a replacement of MOSFETs

Planar bulk transistors have been serving the needs for integrated circuits for several decades. Over the years, the size of the transistors has been decreasing following

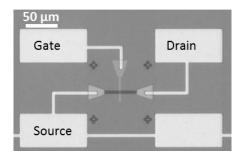

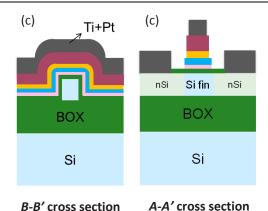

Moore's law [14]. The motivation is saving space and reducing the unit cost. An increase in switching speed (due to shrinking the size of the gate) is a useful by-product of the miniaturization. However, continuous downscaling of these devices leads to an increase in short channel effects (SCE). SCE dominates when channel lengths are comparable to depth of source and drain junctions and depletion widths. It causes a degradation of the sub-threshold characteristics and results in higher standby power consumption [15]. After the introduction by Hisamoto *et al.* [16], the fin-shaped field-effect transistor (FinFET) has attracted much interest to solve this issue. A schematic view of the FinFET with a single fin on a silicon-on-insulator (SOI) substrate is shown in Fig. 1.3.

Fig. 1.3. Schematic layout of an SOI FinFET, bird's eye view.

The FinFET is a potential replacement of the bulk MOSFET. It comprises a gate around silicon (Si) body and depending on its design, it is considered as a double-gate or a triple-gate (this figure) device. With the help of the double-gate or triple-gate architecture, the FinFET enables a better electrostatic gate control over the channel, which comes with relatively low power consumption in standby mode [17, 18]. FinFETs are already a part of the most modern processors.

Furthermore, if the fin body was designed ultra-narrow, it would be entirely depleted enabling volume inversion [19]. The same architecture can also be obtained with a planar SOI FET having an ultra-thin silicon body. A fully depleted body with low doping helps i) to obtain an inverse sub-threshold slope (i.e. subthreshold swing, SS) close to the theoretical value of 60 mV/dec at T=300 K (this will be discussed in section 1.3), ii) to tailor the threshold voltage ( $V_{th}$ ) by adjusting the work function of the gate material only, iii) to reduce the impurity scattering thereby increasing the mobility and iv) to eliminate random dopant fluctuations [20-22]. In addition, since the charge carriers are confined in the body, the effects related to surface imperfections, such as traps, and scattering are less important for ultra-narrow fins. This means that the switching speed and mobility can be increased [23]. However, when the fin width is too small, due to the quantum confinement effect, carrier scattering inside the channel becomes more important than

surface scattering; resulting in a reduced mobility. Therefore, optimum conditions need to be found regarding the device architecture.

Along with its superior properties, the development of the FinFET leads to design and process related requirements like *i*) the threshold voltage adjustment, which requires gate work function tuning around the whole fin, *ii*) fringing capacitance between gate and top/bottom of the source/drain (S/D) regions, which requires minimizing fin pitch and using merged S/D, *iii*) parasitic S/D series resistance, which requires epitaxially raised S/D and silicide engineering and *iv*) performance variability, which requires uniform fin width and gate work function [24-28]. Therefore, the design parameters need to be considered to eliminate or to minimize these effects.

In this work, along with all the advantages mentioned above, the choice of the FinFET-like structure for the PiezoFET with narrow fins is a good candidate to obtain the optimum amount of strain in the Si channel.

FinFETs can be fabricated on SOI or bulk substrates. Up to date, there have been several reports mentioning the advantages of SOI FinFETs over their bulk counterparts [29-31]. Although they are more expensive, SOI substrates and lowly doped fins result in less junction capacitance, high mobility and reduced mismatch [32]. Although self-heating effect is a known problem for SOI devices [33], it will not be an issue for low power device concepts.

In this research, SOI substrates were used to realize FinFETs. The SOI substrates were obtained from NXP Semiconductors, Nijmegen. They were first laser cut from 125 mm to 100 mm to make them compatible with the available systems in the MESA+ Nanolab. More details about the processing and analysis of the fabricated devices are given in chapter 4.

#### 1.3.2 Encapsulated TiN as a gate material

In low power CMOS, a symmetrical and low threshold voltage metal gate is desired for n-channel and p-channel devices [34, 35]. For many years poly-Si has been used as a gate material. The main reason for this is that a heavily doped poly-Si gate can be tailored such that it has work function close to the band edges (*i.e.*  $\approx$ 4.2 eV for n-type and  $\approx$ 5.2 eV for p-type). Its work function can be further modulated by adjusting the doping conditions. This makes it suitable for both n- and p-type devices. Another advantage of the poly-Si gate is the higher temperature budget. However, as a downside, the poly-depletion effect (i.e. creation of depletion layer in the gate, which adds in series to the oxide capacitance) might increase the effective oxide thickness, thereby decreasing the series capacitance and the drive current. In addition, the p+ poly Si gate is not compatible with high- $\kappa$

dielectrics due to Fermi level pinning [36]. Furthermore, the gate sheet resistance of even a heavily doped poly-Si is higher than that of a metal gate. The formation of silicide is used to increase the conductivity to solve this issue. For reducing the gate leakage and not to suffer from partial depletion effects, high- $\kappa$  materials are co-integrated with the gate technology in semiconductor industry.

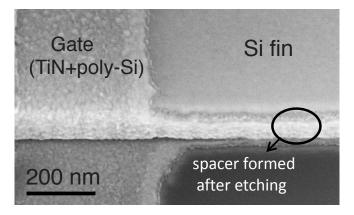

The use of a metal gate eliminates these poly depletion and conductivity problems. However, in general, most metals are not compatible with high temperature processing (>  $600~^{\circ}C$ ). Metal nitrides (in our case TiN), on the other hand, are more suitable for higher temperatures. TiN is encapsulated with a poly-Si layer for planarization purposes and to prevent oxidation. The poly-Si layer also serves as a hard mask for ion implantation. The work function of metal nitrides typically is between 4.4 eV and 4.7 eV. This work function is not suitable for low power planar MOSFETs (it needs to be close to the Si band edge for planar structures) but they can be utilized for low power, multigate CMOS applications [37]. Therefore, in this study, we choose the poly-Si/TiN stack as a gate material for the fabricated SOI FinFET devices, using thermal SiO<sub>2</sub> as the gate dielectric.

#### 1.3.3 Converse piezoelectric effect as a stressor

When an electric field is applied to a piezoelectric material, the structure of the piezoelectric material is deformed mechanically by the converse piezoelectric effect [38]. This deformation will be transferred to the surrounding material. The electrical signal is then transformed into a mechanical or acoustic signal. The use of the converse piezoelectric effect has been reported before for different device structures.

In a bulk acoustic wave or a surface acoustic wave resonator, for instance, the converse piezoelectric effect is used to obtain a resonance [38, 39]. A report from Shayegan *et al*. [40] demonstrated the use of piezoelectric material to apply a uniaxial stress in a plane of a confined 2D electron system formed by an AlAs quantum well. In this way, the electronic properties of the 2D electron system can be modified.

Note that, the piezoelectric effect is widely used in III-V heterojunction device structures. In these devices, lattice mismatch induced strain causes piezoelectric polarization, which results in an increased electron concentration in a 2-dimentional electron gas (2DEG) and a threshold voltage shift [41, 42]. However, to the best of our knowledge there has not been any experimental evidence on the electrical characteristics in these III-V devices caused by the opposite effect, hence the converse piezoelectric effect.

In this study, the converse piezoelectric effect is used for stressing Si FinFET channels [13]. The main objective is to change the transport properties to obtain high mobility and steep

sub-threshold slope devices. Analyses about the strain effect in Si channels are given in chapter 2.

#### 1.4 Technological requirements and research questions

As mentioned before, the objective of this thesis is to realize strained FinFETs with a piezoelectric stressor. There are quite some technological problems:

- i) Fabricating the near-ideal FinFET device structures comprising narrow fin widths with a high aspect ratio to obtain a high amount of strain. This also implies that a combined effort of e-beam lithography and photolithography is required in the MESA+ cleanroom, which is not straightforward,

- *ii)* Growing or depositing high quality, uniform piezoelectric material on top of the FinFET structures,

- *iii*) Optimizing the thickness of the layers between the piezoelectric stressor and the Si channel to a minimum to prevent stress relaxation while maintaining the quality of these layers,

- iv) Integration of the piezoelectric layer without degrading the Si channel.

As a result, many research questions arise:

- *i)* What is the step coverage of the piezoelectric layer around the fin? What is its grain/domain orientation?

- *ii)* Do we maintain good ferroelectric or piezoelectric properties for aggressively scaled dimensions for both the buffer and the piezoelectric layers?

- iii) Can we integrate the piezoelectric layers with Si? This is especially difficult for good piezoelectric materials such as Lead zirconate titanate (PZT). Is there diffusion of contaminants from the PZT layer into the Si body? And, if so, do they affect the device behavior?

- *iv)* What is the effect of the piezoelectric layers on the electrical characteristics of the FinFET? For instance, does it influence the *SS* or mobility as expected? Does it depend on the device dimensions and geometry?

- v) Is the converse piezoelectric effect feasible for significantly stressing the channel?

These subjects are addressed and most of the questions will be answered in the following chapters of this thesis.

#### 1.5 Organization of the thesis

This thesis is organized as follows:

Chapter 2 introduces the use of strain in Si based devices. Strain formation and its effects on the transport properties such as band gap and mobility are discussed. More specifically, FinFETs with a constant strain are presented. Analysis of the strain in these devices has been performed with the help of electrical and optical characterization techniques. The results provide a clear evidence of the effect of strain on the band alignment of Si.

Chapter 3 introduces an experimental study on the sub-100 nm ferroelectric thin film PZT capacitors. The influence of the film thickness and the encapsulated TiN bottom electrode on the ferroelectric and piezoelectric properties of PZT has been investigated. Some important figures-of-merit have been obtained with the help of electrical and optical characterization techniques. These figures have been utilized to optimize the PiezoFET design in this thesis.

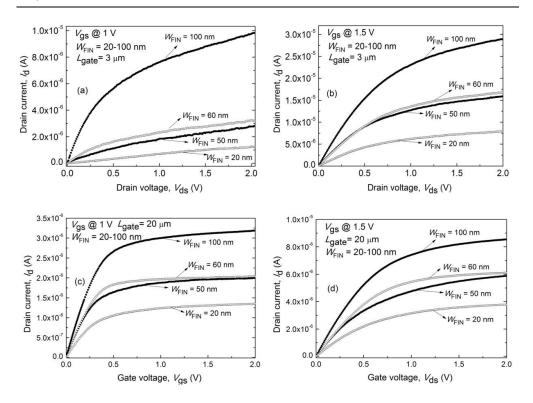

Chapter 4 presents the realization and characterization of FinFETs. FinFETs with different fin widths and channel lengths have been realized to obtain a variable strain configuration after the piezoelectric layer deposition. The presented devices show good electrical characteristics and they provide a basis for the novel device structure called the PiezoFET, in chapter 5.

Chapter 5 describes the novel PiezoFET. It starts with a brief analysis of the piezoelectric layer as a stressor. Details of the device fabrication and characterization are presented. The observed effects in the transport properties of the PiezoFET have been investigated and are discussed. Finally, conclusions are given based on the analysis of the experimental results.

Finally, chapter 6 summarizes this study and presents recommendations for future research.

#### References

- [1] A. P. Chandrakasan, S. Sheng, and R. W. Brodersen, "Low-power CMOS digital design", IEEE Journal of Solid-State Circuits, 27, pp. 473-484, 1992.

- [2] K. Rim, S. Koester, M. Hargrove, J. Chu, K.A Jenkins, P. Mooney, J. Ott, T. Kanarsky, P. Ronsheim, M. leong, and H. S. Wong, "Strained Si NMOSFETs for high performance CMOS technology", IEEE Symposium on VLSI Technology, Digest of Technical Papers, pp. 59-60, 2001.

- [3] J. G. Fiorenza, G. Braithwaite, C. Leitz, M. T.Currie, Z. Y. Cheng, V. K. Yang, T. Langdo, J. Carlin, M. Somerville, A. Lochtefeld, H. Badawi, and H. M. T. Bulsara. "Investigation of misfit dislocation leakage in supercritical strained silicon MOSFETs", Proceedings of 42nd annual IEEE International Reliability Physics Symposium pp. 493-497, 2004.

- [4] T. Khrishnamohan, "Physics and Technology of High Mobility, Strained Germanium Channel Heterostructure MOSFETs" Ph.D. thesis, 2006.

- [5] N. Serra, F. Conzatti, D. Esseni, M. De Michielis, P. Palestri, L. Selmi, S. Thomas, T. E. Whall, E. H. C. Parker, D. R. Leadley, L. Witters, A. Hikavyy, M. J. Hytch, F. Houdellier, E. Snoeck, T. J. Wang, W. C. Lee,

- G. Vellianitis, M. J. H. van Dal, B. Duriez, G. Doornbos, and R. J. P. Lander, "Experimental and physics-based modeling assessment of strain induced mobility enhancement in FinFETs", IEEE International Electron Devices Meeting (IEDM) Technical Digest, pp. 1-4, 2009.

- [6] O. M. Nayfeh, C. N. Chleirigh, J. L. Hoyt, and D. A. Antoniadis, "Measurement of Enhanced Gate-Controlled Band-to-Band Tunneling in Highly Strained Silicon-Germanium Diodes", IEEE Electron Device Letters, 29, pp. 468-470, 2008.

- [7] K. Gopalakrishnan, P. B. Griffin, and J. D. Plummer, "Impact ionization MOS (I-MOS)-Part I: device and circuit simulations" IEEE Transactions on Electron Devices, 52, pp. 69-76, 2005.

- [8] K. Gopalakrishnan, R. Woo, C. Jungemann, P. B. Griffin and J. D. Plummer, "Impact ionization MOS (I-MOS)-Part II: device and circuit simulations" IEEE Transactions on Electron Devices, 52, pp. 77-83, 2005.

- [9] A. Seabaugh, and Q. Zhang, "Low voltage tunnel transistors for beyond-CMOS logic," Proc. of IEEE, 98, pp. 2095-2110, 2010.

- [10] A. M. Ionescu, "Nanoelectronics: Ferroelectric devices show potential", Nature Nanotechnology, 7, p. 83-85, 2012.

- [11] S. Salahuddin, and S. Datta, "Use of Negative Capacitance to Provide Voltage Amplification for Low Power Nanoscale Devices", Nano Lett., 8, pp. 405–410, 2008.

- [12] A. Rusu, G. A. Salvatore, D. Jimenez, and A. M. Ionescu, "Metal-Ferroelectric-Meta-Oxide-semiconductor field effect transistor with sub-60mV/decade subthreshold swing and internal voltage amplification", IEEE International Electron Devices Meeting (IEDM) Technical Digest, 2010.

- [13] T. van Hemert, and R. J. E. Hueting, "Active Strain Modulation in Field Effect Devices", Proc. of the European Solid-State Device Research Conference (ESSDERC), pp. 125-128, 2012.

- [14] G. Moore, "Cramming more components onto integrated circuits", Electronics Magazine, 38 1998.

- [15] S. Dhar, M. Pattanaik, and P. Rajaram "Advancement in Nanoscale CMOS Device Design En Route to Ultra-Low-Power Applications" VLSI Design, 2011, id:178516, 2011.

- [16] D. Hisamoto, W. C. Lee, J. Kedzierski, E. Anderson, H. Takeuchi, K. Asano, T. J. King, J. Bokor, and C. Hu, "A folded channel MOSFET for deep sub tenth micron era", IEEE International Electron Devices Meeting (IEDM) Technical Digest, pp. 1032-1034, 2008.

- [17] X. Wu, F. Wang, and Y. Xie, "Analysis of Subthreshold FinFET Circuits for Ultra-Low Power Design", IEEE SOC conference, pp. 91-92, 2006.

- [18] R. Vaddi, R. P. Agarwal, S. Dasgupta, and T. T. Kim, "Design and Analysis of Double-Gate MOSFETs for Ultra-Low Power Radio Frequency Identification (RFID): Device and Circuit Co-Design", J. Low Power Electron. Appl., 1, pp. 277-302, 2011.

- [19] F. Balestra, S. Cristoloveanu, M. Benachir, J. Brini, and T. Elewa, "Double-gate silicon-on-insulator transistor with volume inversion: A new device with greatly enhanced performance" IEEE Electron Device Letters, 8, pp. 410-412, 1987.

- [20] P. Yeh, and J. Fossum, "Physical sub-threshold MOSFET Modelling Applied to Viable Design of Deep-Submicrometer Fully Depleted SOI Low Voltage CMOS Technology", IEEE Transactions on Electron Devices, 42, pp.1605-1613, 1995.

- [21] Y. Taur, "Analytic Solutions of Charge and Capacitance in Symmetric and Asymmetric Double-Gate MOSFETs", IEEE Transactions on Electron Devices, 48, pp. 2861-2869, 2001.

- [22] H. Tuinhout, "Impact of Parametric Fluctuations on Performance and Yield of Deep-submicron Technologies", Proc. of the European Solid-State Device Research Conference (ESSDERC), pp. 95-102, 2002.

- [23] M. M. Chowdhury, and J. G. Fossum, "Physical insights on electron mobility in contemporary FinFETs", IEEE Electron Device Letters, 27, pp. 482-485, 2006.

- [24] V. Narendar, R. Mishra, S. Rai, Nayana R and R. A. Mishra, "Threshold voltage control schemes in FinFETs" International Journal of VLSI design & Communication Systems (VLSICS), 3, pp.175-191, 2012.

- [25] C. R. Manoj, A. B. Sachid, F. Yuan, C.-Y.Chang, and V. R. Rao, "Impact of Fringe Capacitance on the Performance of Nanoscale FinFETs" IEEE Electron Device Letters, 31, pp. 83-85, 2010.

- [26] A. Dixit, A. Kottantharayil, N. Collaert, and M. Goodwin, "Analysis of the Parasitic S/D Resistance in Multiple-Gate FETs", IEEE Transactions on Electron Devices, 52, pp.1132-1140, 2005.

- [27] A. Sakic, M. Poljak, V. Jovanovic, and T. Suligoj, "Influence of Scaling and Source/Drain Series Resistanceon the Characteristics of Ultra-Thin Body FinFETs", Proceedings of the 31st International Convention MIPRO, 2008.

- [28] T. Matsukawa, S. O'uchi, K. Endo, Y. Ishikawa, H. Yamauchi, Y. X. Liu, J. Tsukada, K. Sakamoto and M. Masahara, "Comprehensive Analysis of Variability Sources of FinFET Characteristics", IEEE Symposium on VLSI Technology Digest of Technical Papers, pp. 118-119, 2009.

- [29] M. Poljak, V. Jovanovic, and T. Suligoj, "Improving bulk FinFET DC performance in comparison to SOI FinFET", Microelectric Engineering, 69, pp. 2078-2085, 2009.

- [30] T. Chiarella, L. Witters, A. Mercha, C. Kerner, M. Rakowski, C. Ortolland, L.-A. Ragnarsson, B. Parvais, A. De Keersgieter, S. Kubicek, A. Redolfi, C. Vrancken, S. Brus, A. Lauwers, P. Absil, S. Biesemans, and T. Hoffmann "Benchmarking SOI and bulk FinFET alternatives for PLANAR CMOS scaling succession", Solid-State Electronics, 54, pp. 855-860, 2010.

- [31] J. G. Fossum, Z. Zhou, L. Mathew, and B. Y. Nguyen," SOI versus bulk-silicon nanoscale FinFETs", Solid State Electronics, 54, pp. 86-89, 2010.

- [32] A. Chiarella, L. Witters, A. Mercha, C. Kerner, R. Dittrich, M. Rakowski, C. Ortolland, L. A. Ragnarsson, B. Parvais, A. De Keersgieter, S. Kubicek, A. Redolfi, R. Rooyackers, C. Vrancken, S. Brus, A. Lauwers, P. Absil, S. Biesemans, and T. Hoffmann, "Migrating from planar to FinFET for further CMOS scaling: SOI or bulk?", Proc. of the European Solid-State Device Research Conference (ESSDERC), pp. 84-87, 2009.

- [33] W. Molzer, Th. Schulz, W. Xiong, R. C. Cleavelin, K. Schrüfer, A. Marshall, K. Matthews, J. Sedlmeir, D. Siprak, G. Knoblinger, L. Bertolissi, P. Patruno, J.-P. Colinge, "Self Heating Simulation of Multi-Gate FETs", Proc. of European Solid-State Device Research Conference (ESSDERC), pp. 311-314, 2006.

- [34] S. J. Hillenius, R. Liu, G. E. Georgiou, R. L. Field, D. S. Williams, A. Kornblit, D. M. Boulin, R. L. Johnston, and W. T. Lynch, "A symmetric submicron CMOS technology", IEEE International Electron Devices Meeting (IEDM) Technical Digest, pp. 252-255, 1986.

- [35] H. R. Huff, and D. C. Gilmer, "High Dielectric Constant Materials, VLSI MOSFET Applications", Springer, 2005.

- [36] C. Hobbs, L. Fonseca, V. Dhandapani, S. Samavedam, B. Taylor, J. Grant, L. Dip, D. Triyoso, R. Hegde, D. Gilmer, R. Garcla, D. Roan, L. Lovejoy, R. Rai, L. Hebert, H. Tseng, B. White and P. Tobin, "Fermi Level Pinning at the PolySi/metal Oxide Interface", IEEE Symposium on Technology, Digest of Technical Papers, pp. 9-10, 2003.

- [37] W. Xiong, C. R. Cleavelin, C.-H. Hsub, M. Ma, K. Schruefer, K. V. Armin, T. Schulz, I. Cayrefourcq, C. Mazure, P. Patruno, M. Kennard, K.Shin, X. Sun, T.-J. King Liu, K. Cherkaoui, and J. P. Colinge, "Intrinsic Advantages of SOI Multiple-Gate MOSFET (MuGFET) for Low Power Applications" ECS Transactions, 6, pp. 59-69, 2007.

- [38] B. A. Auld, "Acoustic fields and waves in solids" 2<sup>nd</sup> ed., Krieger Publishing Company, 1990.

- [39] K. M. Lakin, G. R. Kline, and K. T. McCarron, "High-Q microwave acoustic resonators and filters", IEEE Trans. Microwave Theory and Techn., 41, pp. 2139-2146, 1993.

- [40] M. Shayegan, K. Karrai, Y. P. Skolnikov, K. Vakili, E. P. De Poortere, and S. Manus, "Low-temperature, in situ tunable, uniaxial stress measurements in semiconductors using a piezoelectric actuator", Appl. Phys. Lett., 83, pp. 5235–5237, 2003.

- [41] T. F. Kuech, R. T. Collins, D. L. Smith, and C. Mailhiot, "Field-effect transistor structure based on strain-induced polarization charges", Journal of Applied Physics, 67, pp. 2650-2652, 1990.

- [42] A. Vais, "Physical Simulation of GaN based HEMT", Master Thesis, Chalmers University of Technology, Sweden, 2012.

| Chapter 1 |  |  |

|-----------|--|--|

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

# 2 Strained silicon devices

In this chapter, a brief introduction to strained silicon devices is given. The effect of strain on the band gap and mobility is discussed. The electrical and optical characterization of TiN induced strain on FinFETs is presented. It is demonstrated that the conduction band offset is changing depending on the fin dimensions, which can be explained by counteracting quantum confinement and strain effects.

#### 2.1 Strain formation in silicon-based devices

To improve the transport properties of a (crystalline) semiconductor material, and hence the device performance, so-called strain is often applied in the semiconductor technology and in research projects. Strain is defined as the deformation of a material normalized to its stress free dimension [1]. Strain causes elastic stress (or forces). The strain ( $\varepsilon$ ) and stress ( $\sigma$ ) are related according to the scalar notation  $\sigma = E\varepsilon$ , where E is the stiffness or Young's modulus of the material. Basically, one can imagine the strain effect to be pushing atoms in the periodic crystal together (i.e. compressive or negative strain) or pulling them apart (i.e. tensile or positive strain). This can occur in one direction (uniaxial) only or in several directions (biaxial or triaxial).

There are different ways to form strain in silicon (Si). Some examples are phonon induced lattice vibrations, lattice mismatch during film growth, intrinsic strain in deposited thin films and externally applied strain.

The calculations of Bardeen and Shockley on deformation potentials and the measurements of Smith on the piezoresistance effect are the first physical reports explaining the enhancement of mobility due to strain [2, 3]. Since then, there have been many experimental and theoretical reports on the effect of strain on the band gap and charge carrier mobility [4-11]. Although there was a strong interest in using strained silicon-germanium (SiGe) alloys for high mobility channels, it could not have been realized in Si-based MOSFETs until 1991 due to the high density of interface states generated during oxidation. Iyer et al. [12] were the first who demonstrated a promising high-quality dielectric system by capping the SiGe with a thin Si layer followed by oxide deposition. Later on, Welser et al. [4] first demonstrated an improvement in device performance by strain in n-channel MOSFETs. Here, a strained-Si channel was grown on a relaxed silicongermanium (Si<sub>0.71</sub>Ge<sub>0.29</sub>) layer. Because of the lattice mismatch between the relatively thick SiGe layer and thin Si layer, global biaxial tensile strain has been formed in the latter. In the following years, strained Si/relaxed Si<sub>1-x</sub>Ge<sub>x</sub> systems have been studied extensively and have become a promising candidate for a performance boost in CMOS, mainly by enhancing the mobility [13-16] and consequently the on-current. In addition, some groups reported on the use of Si<sub>1-x</sub>Ge<sub>x</sub> systems in the source and drain regions acting as a local stressor in the channel region for improving the hole mobility in pchannel MOSFETs [17, 18]. This concept is presently in production, for example, in Intel's 45nm Xeon technology.

Along with  $Si_{1-x}Ge_x$ , silicon nitride ( $SiN_x$ ), titanium-nitride (TiN) and piezoelectric materials are also well-known examples for stressors utilized for different purposes.  $SiN_x$  has been studied as an external and local stressor in many studies mainly as a capping layer in

planar and 3D device structures [18-21]. The strain formed by TiN and piezoelectric layers in FinFETs will be discussed in sections 2.3 and 5.1, respectively.

#### 2.2 The effect of strain on the band gap and mobility

Strain is known to change the mobility and modify the band gap of the material depending on the strain type, direction and the material's properties. It is important to note that both the conduction and valence band in Si are degenerate: the first comprises six so-called  $\Delta$  valleys while the latter can be subdivided into a heavy hole (HH) and a light hole (LH) band. When stress is applied, the degeneracy basically becomes less. The changes in conduction and valence band in bulk Si for biaxial tensile strain is shown in Fig. 2.1. Valence band in Fig 2.1 (b) is plotted in energy vs. reciprocal space (or k-space, with  $k=2\pi/l$ attice constant).

Fig. 2.1 Biaxial tensile strain induced changes in the (a) conduction band and (b) valence band of planar/bulk Si. Redrawn after Rim et al. [22].

The Si conduction band valleys split into  $\Delta_2$  and  $\Delta_4$  valleys depending on the amount and orientation (in this case [001] oriented) of stress or strain. On the other hand, the valence

HH band shows a linear while the LH band shows a nonlinear dependency with strain. In case of a large amount of strain, the electrons completely populate the lower  $\Delta_2$  valley [7]. Since the in-plane conductivity effective mass of the  $\Delta_2$  valleys is smaller than that of the  $\Delta_4$  valleys and intervalley scattering is suppressed due to this splitting, the electron mobility increases [23]. Similarly, strain lifts the degeneracy between HH and LH bands and the spin orbit band is lowered in energy resulting less intervalley scattering and improvement in-plane hole mobility. In fact, as indicated in Fig. 2.1 (a) and (b), the conduction band edge drops and valence band edge increases resulting in a reduced band gap.

Skotnicki *et al.* [6] reported the effect of strain on the band gap and mobility of a bulk MOSFET with a <110> oriented channel. Table 2.1 shows a part of this report. The table indicates that the band gap decreases for all stress conditions. However, the net change depends on the presence of quantization effects. The change in mobility, on the other hand, depends on the stress condition. It is observed that tensile stress along the channel length is needed to obtain higher electron mobility. In contrast, it leads to a decrease in hole mobility.

Table 2.1 Analysis of strain configuration and its effects in CMOS (Skotnicki et al. [6], with courtesy).

K. A. Rim *et al.* [24] experimentally showed for the first time that the sub-threshold current of an n-type Si MOSFET increases, or the threshold voltage drops ( by  $\approx$  200mV), when biaxial tensile strain is applied. This is due to this smaller bandgap and lower conduction band in strained Si compared to the relaxed or bulk Si counterpart. In

addition, calculations indicate that both biaxial and uniaxial tensile stress causes a band gap decrease for Si, Ge and GaAs [11]. However, for compressive stress, the band gap changes depending on the stress configuration.

The effect of strain on the mobility of n-MOSFET and p-MOSFET device structures under different stressing conditions has been studied extensively. Depending on the orientation, strain type and level, mobility enhancement was demonstrated in many reports. This helped to understand and to control the effects [5,25,26].

Furthermore, the effects of strain on a material with a thickness of only several atomic layers differ from bulk material. Quantization effects have to be taken into account when dimensions are downscaling. In that case, the band structure and mobility will be affected depending on both the applied strain and quantization. With quantization, the apparent or effective band gap of the material increases [27-29]. This effect is also demonstrated and explained in section 2.3.1.1 for n-type FinFETs. Strain in these devices resulted in an enhancement in mobility and on-current as reported by Rim *et al.* [30] and Feste *et al.* [31]. They demonstrated a 110 % and 230 % improvement in electron mobility in a 7 nm thick planar strained Si layer and 42 nm thick,  $\approx$  35 nm wide strained Si fin, respectively. This resulted in a proportional increase in on-current of the strained FinFET. These figures show that strained FinFET structures are important for CMOS applications.

#### 2.3 TiN induced strain on FinFETs

In section 2.1, several techniques of strain formation have been discussed. This section focusses on the external and local strain formation in FinFETs due to the use of a stiff conductor such as TiN [32-35]. The motivation of using the FinFET configuration was discussed in chapter 1, section 1.3.1.

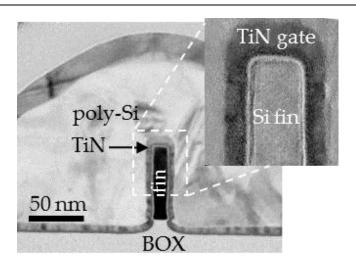

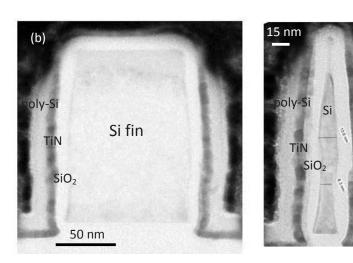

TiN induced strain in Si originates from its growth mechanism and the difference in coefficient of thermal expansion (CTE) between the TiN gate and the Si. This type of strain has been studied before [26, 36, 37] focusing on the mobility. In this work, FinFETs manufactured by NXP-TSMC Research Leuven, Belgium [38], have been studied focusing on the band alignment. The silicon-on-insulator (SOI) FinFETs have a (001) surface and ( $1\overline{1}0$ ) fin sidewall orientation. It is basically the same device set as reported by Serra *et al.* [37] which has been analyzed further. Fig. 2.2 shows a TEM cross section of a FinFET on an SOI substrate. The gate stack consists of a gate dielectric layer with a 1 nm thick silicon-dioxide (SiO<sub>2</sub>) and 1.7 nm thick hafnium-silicate (HfSiO) layer and a 5 nm thick TiN layer (deposited by physical vapor deposition) as the gate material with a poly-Si capping. All the devices characterized in this work comprised five fins with various fin widths (5 nm  $\leq W_{\text{FIN}} \leq 1000 \text{ nm}$ ) and gate lengths (35 nm  $\leq L_{\text{gate}} \leq 10 \text{ µm}$ ). The fin height or SOI thickness was 60nm ( $H_{\text{FIN}}$ ). For more processing details, refer to [38].

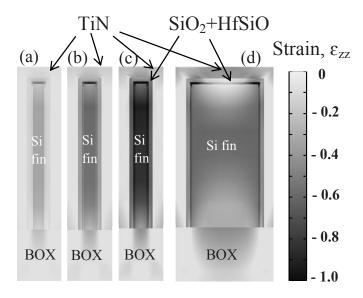

Fig. 2.2 TEM cross section picture of the FinFET (with courtesy of M. van Dal).

An important detail is the thermal cycle implemented after gate deposition. This results in a permanent strain in the channel [37]. This strain can be illustrated by simulations performed using a multiphysics Finite-element-method (FEM) tool (Comsol MultiPhysics 3.5a). In the simulations, the Si substrate was neglected to decrease the computational load. Fixed boundary conditions were applied below the buried oxide (BOX) layer to mimic the stiff Si substrate. For the Young's modulus and CTE of Si and TiN are taken 130 GPa & 2.5x10<sup>-6</sup> K<sup>-1</sup> and 600 GPa & 9.4x10<sup>-6</sup> K<sup>-1</sup>, respectively. The experimental 5-fin device structure was simplified to a single fin device. Symmetric boundary conditions were applied to the sides of the fins as well as at the source and drain regions. The rest of the boundaries were kept free to move. A high temperature cycle from 25 °C to 1100 °C and back to 25 °C has been implemented on the device structure to form strain as in the real case. During the thermal cycle of the stacked structure, the strain increases while the temperature increases. At elevated temperatures (above 1100 °C) plastic relaxation occurs and the strain will be low. The simulations are referenced to this relaxed state. When the system is cooling down, the strain increases again and remains permanently in the Si body or fin. Figs. 2.3 (a)-(c) show the simulated vertical strain  $(\varepsilon_{zz})$  in the fin cross section of a 5 nm wide fin at 900 °C, 500 °C and 25 °C, respectively. Compressive strain  $(\varepsilon_{zz})$  in the range of -0.9 % has been observed for a 5 nm fin width  $(W_{FIN})$ . The other strain components,  $\varepsilon_{xx}$  and  $\varepsilon_{yy}$  are much smaller than  $\varepsilon_{zz}$  (up to -0.18 %) and therefore neglected. The simulation for the 30 nm wide fin at 25 °C is also depicted (Fig. 2.3 (d)) to show that the generated strain decreases when  $W_{\text{FIN}}$  increases. It also becomes less uniform in the silicon body. FEM simulated maximum strain values are plotted against  $W_{\text{FIN}}$  in Fig. 2.10 $^1$ .

<sup>&</sup>lt;sup>1</sup> The simulations were performed by Tom van Hemert, with courtesy.

As demonstrated before by Serra *et al.* [37] compressive strain in the fin height direction favors an increase in electron mobility.

Fig. 2.3  $\varepsilon_{zz}$  strain values of the 30 nm and 5 nm wide FinFETs obtained with multiphysics FEM simulations during cooling down cycle from T=1100 °C to 25 °C for  $W_{\text{FIN}}$ =5 nm at (a) 900 °C, (b) 500 °C, (c) 25 °C, and (d) 25 °C for  $W_{\text{FIN}}$ =30 nm. The vertical bar indicates the strain values varying from 0 to -1.0 (compressive) strain. The thickness of the TiN film is 5 nm and the height of Si fin is 60 nm. Note the relatively high strain value in the HfSiO gate dielectric.

## 2.3.1 Characterization of strain by optical and its effects by electrical techniques

Strain characterization plays an important role in understanding and controlling strain effects. There are different methods possible for this purpose. Raman spectroscopy [39, 40] is mainly used for strain characterization. However, holographic interferometry [37], synchrotron x-ray scattering [41] and nano-beam diffraction [42] techniques have also been used by several research groups. Each of these techniques has advantages and disadvantages regarding the resolution and sensitivity.

In addition to these direct measurement techniques, electrical characterization can also be employed to study the effect of strain in devices. In this case, strain effects are expected to appear as a change in the band gap and mobility as described in section 2.2. Using both optical and electrical characterization and in depth knowledge of strain and its effect can be obtained. In the following two sub-sections, *I-V* curves will be studied to analyze the effect of strain on FinFETs and Raman spectroscopy will be used to characterize the strain.

#### 2.3.1.1 Temperature dependent I-V measurements on strained devices

Temperature dependent I-V measurements were performed using n-type strained FinFET devices with different fin widths ( $W_{\text{FIN}}$ ) and gate lengths ( $L_{\text{gate}}$ ) [32, 34]. By using the subthreshold current technique described by van der Steen et~al. [43] energy band offsets of the FinFETs can be extracted. Since the band offsets depend on the amount of strain, this method can be utilized. As discussed before on our FEM simulations, the amount of strain in the FinFETs under study are expected to increase for a smaller  $W_{\text{FIN}}$ .

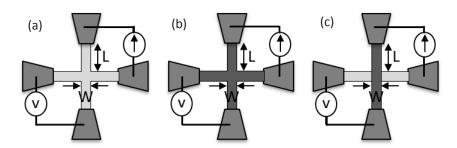

Valence or conduction band offsets can be calculated using the subthreshold current of the reference device having a wide fin (hence negligible strain), namely  $I_{ref}$ , and that of a device with a smaller fin width,  $I_{thin}$ . The ratio of subthreshold currents is then given by:

$$\eta \equiv \frac{I_{ref}}{I_{thin}} = \frac{\mu_{ref,g(W_{FIN,ref})}}{\mu_{thin,g(W_{FIN,thin})}} \exp(\frac{\Delta E_x}{kT})$$

(2.1)

where  $g(W_{\text{FIN}})$  represents the effective density of states (DOS) depending on the fin width,  $\mu$  is the charge carrier mobility, and  $\Delta E_X$  is the difference in conduction or valence band edge of the reference and narrow fin device. Since n-type FinFETs have been studied for this purpose, only the conduction band offset has been determined. In order to determine the valence band offset p-type FinFETs are required. The temperature dependence of  $\eta$  depends strongly on the conduction band offset because of the exponential term. Assuming equal temperature dependence of  $\mu$  and DOS for both devices,  $\Delta E_X$  /k is found to be equal to the slope of the  $\ln(\eta)$  vs. 1/T. It is important to note that the strain changes with temperature. However, this change is small (0.1 %) compared to the overall strain (-0.6 %) [34].

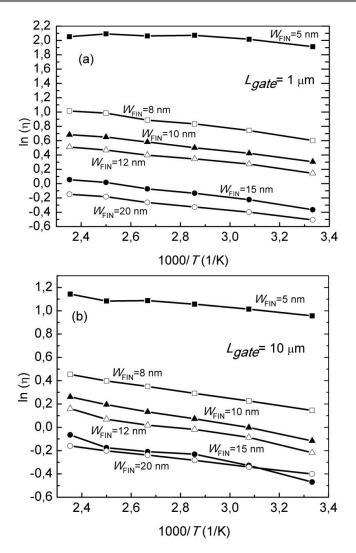

I-V measurements of  $(1\overline{10})/[110]$  oriented n-FinFET devices were done at temperatures ranging from 25 °C to 150 °C. Since short channel effects can result in misinterpretation of the results, the conduction band offset was calculated from long channel devices (i.e. 1 μm and 10 μm). The maximum  $W_{\text{FIN}}$  here was 30 nm, which was used as a reference, and the minimum  $W_{\text{FIN}}$  was 5 nm. In Fig. 2.4  $\ln(\eta)$  vs. 1/T curves have been plotted for the FinFETs with 1 μm and 10 μm gate length.

Fig. 2.4  $ln(\eta)$  vs. 1/T curves of (a) 1  $\mu m$  and (b) 10  $\mu m$  long devices.

In Fig. 2.4 the  $\ln(\eta)$  value increases for narrow fins. This effect is due to a decrease in mobility for very narrow fins [44]. However, this increase is stronger for a 1  $\mu$ m device than that of a 10  $\mu$ m long device. A reason could be a more profound non-uniformity in channel width and parasitic charges, since at low vertical fields Coulomb scattering is important.

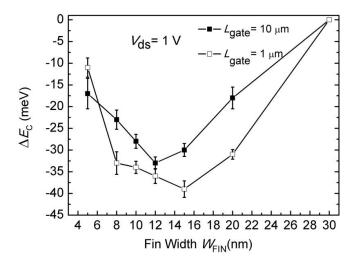

From the slope of the curves depicted in Fig. 2.4, the calculated conduction band offset has been plotted against  $W_{\text{FIN}}$  as shown in Fig. 2.5. Values down to  $\approx$  -40 meV are obtained. The error bars in Fig. 2.5 were determined from the error associated with linear fitting of  $\ln(\eta)$  vs. 1/T curves. In this figure, a maximum value for the (absolute) band offset has been obtained for a  $W_{\text{FIN}}$  of around 12 nm. This can be explained by two

counteracting mechanisms [32, 34]. As discussed earlier, when  $W_{\text{FIN}}$  is decreasing, the built-in strain due to the TiN layer increases. For all strain conditions this shifts the lowest occupied conduction band, hence the  $\Delta_2$  valleys, downwards with respect to un-strained condition [37]. However, for  $W_{\text{FIN}} < 12$  nm, quantization of the carriers occurs and this results in an upward shift of the conduction band edge (despite the higher amount of strain). The same trend was obtained by van Hemert *et al.* [34] in their band offset calculations in which strain and quantization effects were taken into account. Note that the impact of these effects depends on the channel orientation [34], in our case the channel is oriented along [110] direction.

Fig. 2.5 Extracted conduction band offset for a device with a 1  $\mu m$  and 10  $\mu m$  gate length.

#### 2.3.1.2 Raman spectroscopy characterization of strain

A more direct physical characterization technique would complete the strain analysis and could be helpful to support the observations in the electrical data obtained from the NXP-TSMC FinFETs. Raman spectroscopy is a non-contact and non-destructive technique that is most widely employed for this purpose [35, 39, 45-48], yielding valuable information about strain even in aggressively scaled device configurations [40, 49].

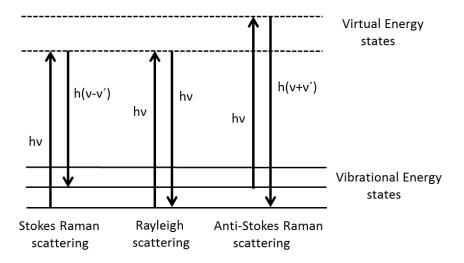

The technique relies on the inelastic scattering, or Raman scattering, of monochromatic light (usually from a laser). The scattering process involves an instantaneous absorption of a photon and subsequent emission of scattered photon. When the emitted photon is elastically scattered, the incident and scattered photon has the same frequency. However, if an inelastic scattering occurs, the frequency of the scattered photon shifts. During inelastic scattering, incident photons excite atom or molecule from the ground to a virtual energy level. While relaxing, it emits a photon and returns to a different rotational or vibrational state. Depending on the energy of the final state with respect to

initial state, the emitted photons of the laser light will be shifted to higher or lower frequency. This shift provides information about the vibrational, rotational and other transitions. However, inelastic scattering (or Raman scattering) results in a weak signal while the intense part of the signal is due to elastic scattering (or Rayleigh scattering). Therefore, the Rayleigh scattered photons are filtered out to separate the weak Raman scattered photons. Fig. 2.6 illustrates the transitions corresponding to Rayleigh scattering, stokes and anti-Stokes Raman scattering.

Fig. 2.6 A diagram illustrating the transitions corresponding to Rayleigh scattering, Stokes and anti-Stokes Raman scattering.

When the crystal lattice is mechanically strained, the atomic distances change. Since the lattice vibration frequency depends on the atomic distance, a vibrational frequency shift occurs. This shift directly affects the Raman peak position. Strain level in the lattice can be determined by using the calibrated Raman peak shift-strain relation.

The Raman spectroscopy measurements have been carried out at room temperature using a confocal Raman microscope (alpha300R, Witech GmbH) with 0.8 cm<sup>-1</sup> wavenumber resolution (which corresponds to about 0.15 % strain resolution) and a 532 nm laser source with an output power of 47 mW. This wavelength will give a penetration depth of light in the silicon in the range of 800-1000 nm. This high penetration depth leads to a weak Raman signal from the FinFET with respect to the strong signal from the surrounding relaxed silicon. It is important to note that, since a high penetration depth might be an issue, we performed Raman measurements on the same samples at a shorter wavelength (454 nm) using the Renishaw Raman tool<sup>2</sup>. In that case, we obtained less significant strain peaks. The wavenumber resolution was relatively low and a lower signal

24

<sup>&</sup>lt;sup>2</sup> These measurements were performed with Emile Verstegen (Philips, Eindhoven), with courtesy.

was obtained from the strained-Si region. The penetration depth of the 454 nm laser in Si is around 300 nm, but due to the TiN and poly-Si layers on top of the Si, the signal could not be obtained from the whole strained Si volume. Therefore, although a laser with 532 nm wavelength had a high penetration depth, we got more signal from the Si fin compared to a laser with a 454 nm wavelength. Hence, for our analysis the 532 nm laser is a better choice.

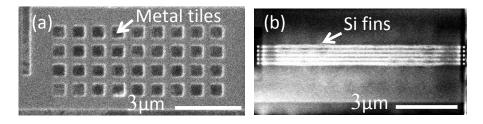

Metallic tiles were on top of the FinFET structures. The metal layers were very thick and blocking the light. Therefore, they were removed using Focused Ion Beam (FIB) milling. Removal of these layers was necessary to obtain a good Raman signal from the area of interest. Fig. 2.7 shows the HR-SEM picture of a device before and after FIB removal of the metal layers. To prevent the damage to the stressor TiN layer, FIB process parameters were optimized at a 47 pA beam current and a process time of 5 minutes. A cross sectional SEM image after FIB processing confirmed that the stressor layer was still present. Raman spectroscopy on these samples was done by scanning the complete area of the channel region.

Fig. 2.7 HR-SEM image of a device before (a) and after (b) FIB removal of the metal layers.

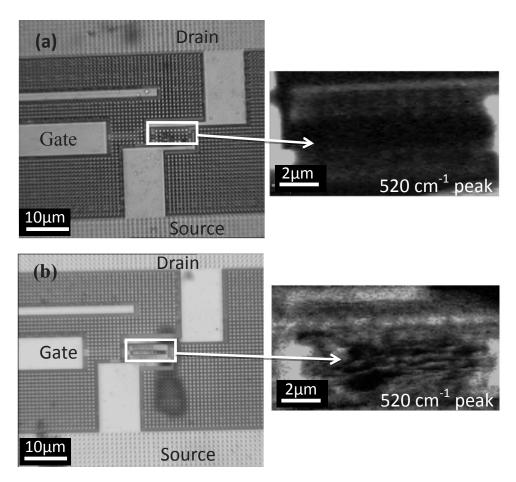

Fig. 2.8 shows the peak map of the scanned device region before and after the FIB process. It is clearly observable that the Raman peak of the Si channel region is only detectable after the FIB process. To identify the Si channel from this map, the Raman peak at 520 cm<sup>-1</sup> is highlighted. The contrast in this figure indicates different peaks of the Raman spectrum obtained from the channel. This map helps us to identify the Si fin region from the rest of the substrate and it was used for extracting the Raman spectrum of the strained channel region.

Fig. 2.8 Raman peak map of the channel region (a) before FIB, (b) after FIB preparation. The images on the right side show the peak position map of the Raman spectrum. The 520 cm<sup>-1</sup> peak is highlighted with grey tones to identify the Si channel region from the BOX.

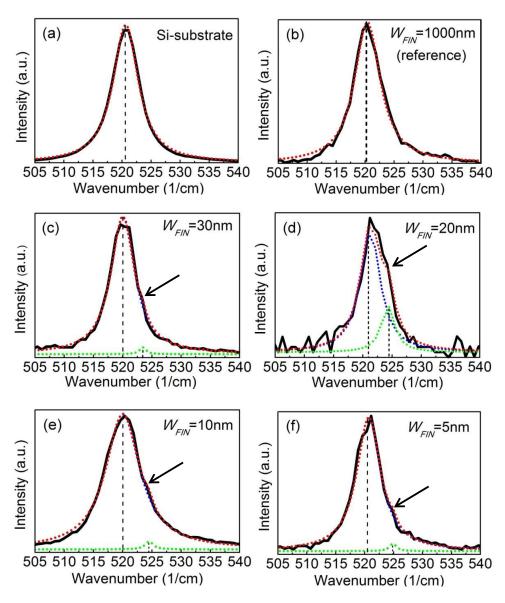

The devices with 10  $\mu$ m gate length and different fin widths were used for measurements after FIB preparation. The samples have been analyzed by fitting the obtained Raman peaks with a Lorentzian function. The measurements are shown in Fig. 2.9.

Fig. 2.9 Obtained Raman spectra of (a) the substrate, and that of the FinFET with a fin width of (b) 1000 nm, used as a reference, (c) 30 nm, (d) 20 nm, (e) 10 nm, (f) 5 nm. The blue dotted curves are the obtained Lorentzian fits corresponding to Si substrate. The green dotted curves are after fitting the second peak due to increased strain also indicated by the arrows to guide the eye. The total fits are indicated by red dotted curves.

In Fig. 2.9 (a) the Si substrate peak is shown. In Fig. 2.9 (b), the peak from the 5-fin FinFET device with  $W_{\text{FIN}}$ =1000 nm is presented. Since the Si-fin layer is only 60 nm thick and the penetration depth of the laser is larger than the sum of the Si fin and BOX layer thickness (≈ 340 nm), the substrate peak as well as the thin un-doped Si peak is present in the Raman spectrum. However, both Raman peaks are from Si and they appear almost at the same wavenumber without stress (i.e. 520 cm<sup>-1</sup>). Therefore, it is not possible to differentiate them. This spectrum is used as a reference for strain calculations. Figs. 2.9 (c)-(f) show a second peak next to the substrate peak in the spectrum. The second peak is from the strained Si fin. It can be seen from Fig. 2.9 that the Si fin peak shifts to higher wavenumbers when the fin width is decreasing from 30 nm to 5 nm. The shift to higher wavenumbers is an indication of compressive stress [50]. Since the stress is much lower for the 1000 nm wide fin device, this second, stressed, Si peak cannot be observed. The first peaks are broadened because of the signal from the poly-Si layer on top of the fins [51]. The strained Si peak is weak compared to the substrate peak since the signal from the surroundings is 15-80 times bigger than that of the strained silicon fins. Therefore, for such a sample, it is quite difficult to get a significant signal from strained silicon but could still be used for the analysis.

The strain values were calculated from the Raman peak shift using the 1000 nm wide fin peak in Fig. 2.9 (b) as a reference. The calculations are dependent on the stress calibration using Raman shift data and the fitting of the peaks. In this way, the strain level and its evolution by fin width is provided. The strain was calculated using the Raman shift according to the following relations [51]:

$$\sigma = -250 (MPa \cdot cm) \cdot \Delta \omega \tag{2.2}$$

$$\varepsilon = \frac{\sigma}{E} \tag{2.3}$$

where E = Young's modulus,  $\sigma$  = stress,  $\varepsilon$  = strain,  $\Delta \omega$  = peak shift.

The Young's modulus of silicon along the z axis is taken as  $E_z$  =130 GPa [52] for the strain calculations. Table 2.2 shows the peak positions and calculated strain values for each device.

Table 2.2: Strain values obtained from a Lorentzian peak fit.

|                | 1                                 |            |

|----------------|-----------------------------------|------------|

| Fin width (nm) | Peak Position (cm <sup>-1</sup> ) | Strain (%) |

| 1000           | 520.3                             | reference  |

| 30             | 523.4                             | -0.60      |

| 20             | 524.2                             | -0.75      |

| 10             | 524.5                             | -0.80      |

| 5              | 524.9                             | -0.88      |

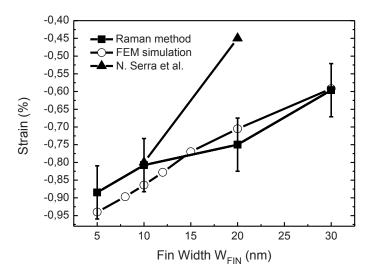

Fig. 2.10 shows the extracted strain values using the Raman shift data together with the strain values obtained by N. Serra *et al.* [37]. The authors used the holographic interferometry method on a similar set of devices to obtain strain information. The strain value obtained for  $W_{\text{FIN}}$ =10 nm with the Raman spectroscopy method is comparable to Serra's results while for  $W_{\text{FIN}}$ =20 nm our results indicates a larger strain value. The strain dependency on the fin width is clearly observed in both sets of data. Furthermore, Fig. 2.10 shows that the maximum strain values obtained from FEM simulations (see also section 2.3) agree well with the Raman spectroscopy data for a wide range of fin widths.

Fig. 2.10 Extracted strain values in silicon FinFETs using Raman spectroscopy. For comparison, FEM simulation and experimental data obtained from the holographic interferometry method [37] have been plotted in the same graph. Note that, due to the limitation of the Raman microscope system, the strain resolution is about 0.15 % for the Raman method.

#### 2.3.2 Discussion

Compressive strain in Si fin height direction is known to move the  $\Delta_2$  valleys down, resulting in a decrease in the band gap of (110) oriented Si [9]. However, the band offset has never been experimentally studied in FinFETs. In section 2.3.1.1 the electrical measurements reveal that there is indeed a downward shift of the conduction band edge when the fin width is decreasing down to about 12 nm. Below this value, quantum confinement has a counteractive effect. In addition, the results obtained from optical measurements in section 2.3.1.2 show that strain is increasing for narrow fins. This is in line with the electrical data as well as holographic measurements and FEM simulations. Good agreement in the extracted strain values was obtained from Raman measurements FEM simulations and holographic interferometry. This indicates that Raman spectroscopy is a good method to obtain actual strain values in FinFET structures with nanometer dimensions. Furthermore, results obtained by these analyses can be used to explain the electrical measurements.

### 2.4 Conclusions

In this chapter, a brief introduction to strain, its use and methods in silicon-based devices, and its effect on band gap and mobility in solids is given. To characterize the strain at device level, temperature dependent I-V measurements and Raman spectroscopy technique were utilized for  $(1\overline{10})/[110]$  oriented n-type strained FinFETs. Both techniques provided valuable information about the conduction band offset and strain level in a nanoscale device structure such as the FinFET.

The electrical results indicate that the conduction band energy offset, reaching values down to  $\approx$  -40 meV, depends on the dimensions of the fin. This is explained by the superposition of two effects: (1) an increase in compressive strain in the fin height direction for smaller fins moving the  $\Delta_2$  valleys downward and (2) quantum confinement for fin widths below 12 nm, separating the energy levels available to electrons and moving the conduction band valleys upward.

A relatively small active device area of interest as well as high penetration depth causes a limitation for FinFET type device measurements with Raman spectroscopy. Despite this fact, reasonable results were obtained. It was shown that Raman peaks from Si fins shift to higher wavenumbers for narrow fins indicating compressive strain. Up to -0.88 % strain has been calculated from our Raman spectroscopy data. FEM simulations and holographic interferometry method were found to point out the same effect which leaded to the results obtained by electrical measurements. These are an indication that Raman

spectroscopy is an effective method to get strain information, even for small (nanoscale) regions of interest.

## References

- [1] D. R. Lovett, "Tensor Properties of Crystals", Adam Hilger, 1989.

- [2] J. Bardeen, W. Shockley, "Deformation Potentials and Mobilities in Non-Polar Crystals", Physical Review, 80, pp. 72-80, 1950.

- [3] S. C. Smith, "Piezoresistance Effect in Germanium and Silicon", Physical Review, 94, pp. 42-49, 1954.

- [4] J. Welser, J. L. Hoyt, J. F. Gibsons, "NMOS and CMOS transistors fabricated in strained silicon/relaxed silicon-germanium structures", Technical Digest International Electron Devices Meeting (IEDM), pp. 1000-1002, 1992.

- [5] T. Mizuno, S. Takagi, N. Sugiyama, H. Satake, A. Kurobe, and A. Toriumi, "Electron and hole mobility enhancement in strained-Si MOSFET's on SiGe-on-insulator substrates fabricated by SIMOX technology", IEEE Electron Device Letters, 21, pp. 230-232, 2000.

- [6] T. Skotnicki, C. Fenouillet-Beranger, C. Gallon, F. Buf, S. Monfray, F. Payet, A. Pouydebasque, M. Szczap, A. Farcy, F. Arnaud, S. Clerc, M. Sellier, A. Cathignol, J. –P. Schoellkopf, E. Perea, R. Ferrant, and H. Mingam, "Innovative Materials, Devices, and CMOS Technologies for Low-Power Mobile Multimedia", IEEE Transactions on Electron Devices, 55, pp. 96-130, 2008.

- [7] F. Rochette, M. Casse, M. Mouis, A. Haziot, T. Pioger, G. Ghibaudo, F. Boulanger, "Piezoresistance effect of strained fully depleted silicon-on-insulator MOSFETs integrating a HfO2/TiN gate stack", Solid-State Electronics, 53, 3, pp. 392-396, 2009.

- [8] S. Flachowsky, A. Wei, R. Illgen, T. Herrmann, J. Hontschel, M. Horstmann, W. Klix, and R. Stenzel, "Understanding Strain-Induced Drive-Current Enhancement in Strained-Silicon n-MOSFET and p-MOSFET", IEEE Transactions on Electron Devices, 57, pp. 1343-1354, 2010.

- [9] N. Serra, and D. Esseni, "Mobility Enhancement in Strained n-FinFETs: Basic Insight and Stress Engineering", IEEE Transactions on Electron Devices, 57, pp. 482-490, 2010.

- [10] T. K. Kang, "Evidence for Silicon Band gap Narrowing in Uniaxially Strained MOSFETs Subjected to Tensile and Compressive Stress", IEEE Electron Device Letters, 33, pp. 770-772, 2012.

- [11] Y. Sun, S. E. Thompson, T. Nishida, "Strain effect in semiconductors, Theory and device applications", Springer 2010.

- [12] S. S. Iyer, P. M. Solomon, V. P. Kesan, A. A. Bright, J. L. Freeouf, T. N. Nguyen, and A. C. Warren, "A gate-quality dielectric system for SiGe metal-oxide-semiconductor devices", IEEE Electron Device Letters, 12, pp. 246-248, 1991.

- [13] H.M. Manasevit, I.S. Gergis, A.B. Jones, "Electron mobility enhancement in epitaxial multilayer Si-Si<sub>1-</sub>  $_{x}$ Ge $_{x}$  alloy films on (100) Si", Applied Physics Letters, 41, 5, 1982, pp. 464-466.

- [14] J. L. Hoyt, H. M. Nayfeh, S. Eguchi, I. Aberg, G. Xia, T. Drake, E. A. Fitzgerald, and D. A. Antoniadis, "Strained silicon MOSFET technology", Technical Digest International Electron Devices Meeting (IEDM), pp. 23-26, 2002.

- [15] W. S. Yoo, T. Ueda, and K. Kang, "Characterization of uni-axially stressed Si and Ge concentration in  $Si_{1-x}Ge_x$  using polychromator-based multi-wavelength Raman spectroscopy", International Workshop on Junction Technology, pp. 78-83, 2009.

- [16] Ji-Song Lim, S.E. Thompson, J.G. Fossum, "Comparison of threshold voltage shifts for uniaxial and biaxial tensile stressed n-MOSFETs", IEEE Electron Device Letters, 25, pp. 731-733, 2004.

- [17] T. Ghani, M. Armstrong, C. Auth, M. Bost, P. Charvat, G. Glass, T. Hoffmann, K. Johnson, C. Kenyon, J. Klaus, B. McIntyre, K. Mistry, A. Murthy, J. Sandford, M. Silberstein, S. Sivakumar, P. Smith, K. Zawadzki, S. Thompson, and M. Bohr, "A 90nm high volume manufacturing logic technology